# $\mathsf{NuDAQ}^{\mathbb{R}}$

ACL-8112 Series Enhanced Multi-Function Data Acquisition Card User's Guide

©Copyright 2003 ADLINK TECHNOLOGY INC.

All Rights Reserved.

Manual Rev. 3.61: October 14, 2003

Part No.: 50-11012-201

The information in this document is subject to change without prior notice in order to improve reliability, design, and function and does not represent a commitment on the part of the manufacturer.

In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or inability to use the product or documentation, even if advised of the possibility of such damages.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

#### Trademarks

NuDAQ and ACL-8112 are registered trademarks of ADLINK TECHNOLOGY INC.. Other product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

# **Getting Service from ADLINK**

Customer Satisfaction is top priority for ADLINK TECHNOLOGY INC. If you need any help or service, please contact us.

| ADLINK TECHNOLOGY INC. |                               |               |                   |  |

|------------------------|-------------------------------|---------------|-------------------|--|

| Web Site               | http://www.adlinktech.com     |               |                   |  |

| Sales & Service        | Service@adlinktech.com        |               |                   |  |

| TEL                    | +886-2-82265877               | FAX           | +886-2-82265717   |  |

| Address                | 9F, No. 166, Jian Yi Road, Ch | ungho City, T | aipei, 235 Taiwan |  |

Please email or FAX your detailed information for prompt, satisfactory, and consistent service.

| D                      | etailed Compan                                                              | y Information |  |

|------------------------|-----------------------------------------------------------------------------|---------------|--|

| Company/Organization   |                                                                             |               |  |

| Contact Person         |                                                                             |               |  |

| E-mail Address         |                                                                             |               |  |

| Address                |                                                                             |               |  |

| Country                |                                                                             |               |  |

| TEL                    |                                                                             | FAX           |  |

| Web Site               |                                                                             |               |  |

|                        | Questi                                                                      | ons           |  |

| Product Model          |                                                                             |               |  |

| Environment            | OS:<br>Computer Brand:<br>M/B:<br>Chipset:<br>Video Card:<br>NIC:<br>Other: | CPU:<br>BIOS: |  |

| Detail Description     |                                                                             |               |  |

| Suggestions for ADLINK |                                                                             |               |  |

# **Table of Contents**

| Chap                                                          | ter 1 In                                                                                                                                                      | troduction                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                              |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 1.1                                                           | Feature                                                                                                                                                       | S                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                                                              |

| 1.2                                                           | Applicat                                                                                                                                                      | ions                                                                                                                                                                                                                                                                                                                                                                                        | 4                                                                                                              |

| 1.3                                                           | Specific                                                                                                                                                      | ations                                                                                                                                                                                                                                                                                                                                                                                      | 4                                                                                                              |

| 1.4                                                           | Softwar                                                                                                                                                       | e Support                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

|                                                               | 1.4.1                                                                                                                                                         | Programming Library                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |

|                                                               | 1.4.2                                                                                                                                                         | LabView Driver                                                                                                                                                                                                                                                                                                                                                                              | 8                                                                                                              |

| Chap                                                          | ter 2 In                                                                                                                                                      | stallation                                                                                                                                                                                                                                                                                                                                                                                  | 9                                                                                                              |

| 2.1                                                           | What Yo                                                                                                                                                       | ou Have                                                                                                                                                                                                                                                                                                                                                                                     | 9                                                                                                              |

| 2.2                                                           |                                                                                                                                                               | ing                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |

| 2.3                                                           |                                                                                                                                                               | 12 <sup>′</sup> s Layout                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |

| 2.4                                                           | Jumper                                                                                                                                                        | and DIP Switch Description                                                                                                                                                                                                                                                                                                                                                                  | 13                                                                                                             |

| 2.5                                                           | Base Ac                                                                                                                                                       | ddress Setting                                                                                                                                                                                                                                                                                                                                                                              | 13                                                                                                             |

| 2.6                                                           |                                                                                                                                                               | Input Channel Configuration                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

| 2.7                                                           |                                                                                                                                                               | nannel Setting                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |

| 2.8                                                           |                                                                                                                                                               | External Trigger Setting                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |

| 2.9                                                           |                                                                                                                                                               | ource Setting                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                |

| 2.10                                                          | IRQ Lev                                                                                                                                                       | vel Setting                                                                                                                                                                                                                                                                                                                                                                                 | 18                                                                                                             |

| 2.11                                                          | D/A Ref                                                                                                                                                       | erence Voltage Setting                                                                                                                                                                                                                                                                                                                                                                      | 19                                                                                                             |

| 2.12                                                          |                                                                                                                                                               | ut Range Setting                                                                                                                                                                                                                                                                                                                                                                            | 20                                                                                                             |

| 2.12                                                          | A/D Inp                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                             | 20                                                                                                             |

|                                                               |                                                                                                                                                               | gnal Connections                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                |

|                                                               | oter 3 Si                                                                                                                                                     | gnal Connections                                                                                                                                                                                                                                                                                                                                                                            | 21                                                                                                             |

| Chap                                                          | oter 3 Si<br>Connec                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                             | <b>21</b>                                                                                                      |

| <b>Chap</b><br>3.1                                            | oter 3 Si<br>Connec<br>Analog                                                                                                                                 | gnal Connections                                                                                                                                                                                                                                                                                                                                                                            | <b>21</b><br>22<br>25                                                                                          |

| <b>Chap</b><br>3.1<br>3.2                                     | o <b>ter 3 Si</b><br>Connec<br>Analog<br>Analog<br>Digital I/                                                                                                 | gnal Connections<br>tors Pin Assignment<br>Input Signal Connection<br>Output Signal Connection                                                                                                                                                                                                                                                                                              | <b>21</b><br>22<br>25<br>28<br>28                                                                              |

| Chap<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                       | oter 3 Si<br>Connec<br>Analog<br>Digital I/<br>Timer /                                                                                                        | gnal Connections<br>tors Pin Assignment<br>Input Signal Connection<br>Output Signal Connection<br>O Connection<br>Counter Connection                                                                                                                                                                                                                                                        | <b>21</b><br>22<br>25<br>28<br>28<br>28<br>29                                                                  |

| Chap<br>3.1<br>3.2<br>3.3<br>3.4                              | ter 3 Si<br>Connec<br>Analog<br>Digital I<br>Timer /<br>Daughte                                                                                               | gnal Connections<br>tors Pin Assignment<br>Input Signal Connection<br>Output Signal Connection<br>O Connection<br>Counter Connection<br>er Board Connection                                                                                                                                                                                                                                 | <b>21</b> 22 25 28 28 28 29 30                                                                                 |

| Chap<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                       | ter 3 Si<br>Connec<br>Analog<br>Digital I/<br>Timer /<br>Daughte<br>3.6.1                                                                                     | gnal Connections<br>tors Pin Assignment<br>Input Signal Connection<br>Output Signal Connection<br>O Connection<br>Counter Connection<br>er Board Connection<br><i>Connect with ACLD-8125</i>                                                                                                                                                                                                | <b>21</b> 22 25 28 28 28 29 30 30 30                                                                           |

| Chap<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                       | ter 3 Si<br>Connec<br>Analog<br>Digital I/<br>Timer /<br>Daughte<br>3.6.1<br>3.6.2                                                                            | gnal Connections<br>tors Pin Assignment<br>Input Signal Connection<br>Output Signal Connection<br>O Connection<br>Counter Connection<br>er Board Connection<br><i>Connect with ACLD-8125</i><br><i>Connect with ACLD-9137</i>                                                                                                                                                               | <b>21</b> 22 25 28 28 29 30 30 30 30 30 30 30 30 30 30 30 30 30                                                |

| Chap<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                       | ter 3 Si<br>Connec<br>Analog<br>Digital I<br>Timer /<br>Daughte<br>3.6.1<br>3.6.2<br>3.6.3                                                                    | gnal Connections<br>tors Pin Assignment<br>Input Signal Connection<br>Output Signal Connection<br>O Connection<br>Counter Connection<br>er Board Connection<br><i>Connect with ACLD-8125</i><br><i>Connect with ACLD-9137</i><br><i>Connect with ACLD-9182</i>                                                                                                                              | <b>21</b> 22 25 28 28 29 30 30 30 30 30 30 30                                                                  |

| Chap<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                       | ter 3 Si<br>Connec<br>Analog<br>Digital I<br>Timer /<br>Daughte<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4                                                           | gnal Connections<br>Input Signal Connection<br>Output Signal Connection<br>O Connection<br>Counter Connection<br>er Board Connection<br>Connect with ACLD-8125<br>Connect with ACLD-9137<br>Connect with ACLD-9182<br>Connect with ACLD-9185                                                                                                                                                | <b>21</b> 22 25 28 28 29 30 30 30 30 30 30 30 30 30 30 30 30 30                                                |

| Chap<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                       | ter 3 Si<br>Connec<br>Analog<br>Digital I<br>Timer /<br>Daughte<br>3.6.1<br>3.6.2<br>3.6.3                                                                    | gnal Connections<br>tors Pin Assignment<br>Input Signal Connection<br>Output Signal Connection<br>O Connection<br>Counter Connection<br>er Board Connection<br><i>Connect with ACLD-8125</i><br><i>Connect with ACLD-9137</i><br><i>Connect with ACLD-9182</i>                                                                                                                              | <b>21</b> 22 25 28 28 29 30 30 30 30 30 30 30 30 30 30 30 30 30                                                |

| Chap<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                | ter 3 Si<br>Connec<br>Analog<br>Digital <i>I</i><br>Timer /<br>Daughte<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5                                           | gnal Connections<br>Input Signal Connection<br>Output Signal Connection<br>O Connection<br>Counter Connection<br>er Board Connection<br>Connect with ACLD-8125<br>Connect with ACLD-9137<br>Connect with ACLD-9182<br>Connect with ACLD-9185                                                                                                                                                | <b>21</b> 22 25 28 28 29 30 30 30 30 30 30 30 30 30 30 30 30 30                                                |

| Chap<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                | oter 3 Si<br>Connec<br>Analog<br>Digital I/<br>Timer /<br>Daughte<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>oter 4 Re                                   | gnal Connections<br>tors Pin Assignment<br>Input Signal Connection<br>Output Signal Connection<br>/O Connection<br>Counter Connection<br>Connect with ACLD-8125<br>Connect with ACLD-9137<br>Connect with ACLD-9182<br>Connect with ACLD-9185<br>Connect with ACLD-9188                                                                                                                     | 21<br>22<br>25<br>28<br>28<br>29<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30 |

| Chap<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>Chap        | oter 3 Si<br>Connec<br>Analog<br>Digital I/<br>Timer /<br>Daughte<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>oter 4 Re<br>I/O Port<br>A/D Dat            | gnal Connections         Input Signal Connection         Output Signal Connection         Output Signal Connection         Connection         Connection         Connection         Connect with ACLD-8125         Connect with ACLD-9137         Connect with ACLD-9182         Connect with ACLD-9185         Connect with ACLD-9188         egisters         Address         a Registers | 21<br>22<br>25<br>28<br>28<br>29<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30 |

| Chap<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>Chap<br>4.1 | oter 3 Si<br>Connec<br>Analog<br>Digital I/<br>Timer /<br>Daughte<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>oter 4 Re<br>I/O Port<br>A/D Dat<br>A/D Cha | gnal Connections         Input Signal Connection         Output Signal Connection         Output Signal Connection         Connection         Connection         Connection         Connect with ACLD-8125         Connect with ACLD-9137         Connect with ACLD-9182         Connect with ACLD-9185         Connect with ACLD-9188                                                      | 21<br>22<br>25<br>28<br>28<br>29<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30<br>30 |

| 4.5<br>4.6<br>4.7 | A/D Operation Mode Control Register<br>Interrupt Status Register | .38 |

|-------------------|------------------------------------------------------------------|-----|

| 4.7<br>4.8        | Software Trigger Register<br>Digital I/O register                |     |

| 4.0<br>4.9        | D/A Output Register                                              |     |

| 4.10              | Internal Timer/Counter Register                                  |     |

| 4.10              |                                                                  | .41 |

| Chap              | oter 5 Operation Theory                                          |     |

| 5.1               | A/D Conversion                                                   | .43 |

|                   | 5.1.1 A/D Conversion Procedure                                   |     |

|                   | 5.1.2 A/D Trigger Modes                                          | .44 |

|                   | 5.1.3 A/D Data Transfer Modes                                    | .45 |

| 5.2               | D/A Conversion                                                   |     |

| 5.3               | Digital Input and Output                                         |     |

| 5.4               | Timer/Counter Operation                                          | .47 |

| Chan              | oter 6 Calibration & Utilities                                   | 51  |

|                   |                                                                  |     |

| 6.1               | What do you need                                                 |     |

| 6.2               | VR Assignment                                                    |     |

| 6.3               | D/A Adjustment                                                   |     |

|                   | 6.3.1 D/A CH1 calibration<br>6.3.2 D/A CH2 calibration           |     |

| 6.4               | A/D Programmable Gain Amplifier adjustments                      |     |

| 6.5               | A/D Adjustment                                                   |     |

| 0.5               | 6.5.1 Bipolar Calibration                                        |     |

|                   | 6.5.2 Unipolar Calibration(Only for ACL-8112DG/HG)               |     |

|                   |                                                                  | .07 |

| Chap              | oter 7 C Language Library                                        | 55  |

| 7.1               | _8112_Initial                                                    | .56 |

| 7.2               | 8112_Switch_Card_No                                              |     |

| 7.3               |                                                                  | .59 |

| 7.4               | _8112_DI _Channel                                                | .60 |

| 7.5               | _8112_DO                                                         | .61 |

| 7.6               | _8112_DA                                                         | .62 |

| 7.7               | _8112_AD_Input_Mode                                              |     |

| 7.8               | _8112_AD_Set_Channel                                             |     |

| 7.9               | _8112_AD_Set_Range                                               |     |

| 7.10              | _8112_AD_Set_Mode                                                |     |

| 7.11              | _8112_AD_Soft_Trig                                               |     |

| 7.12              | _8112_AD_Aquire                                                  |     |

| 7.13              | _8112_CLR_IRQ                                                    |     |

| 7.14              | _8112_AD_DMA_Start                                               |     |

| 7.15              | _8112_AD_DMA_Status                                              |     |

| 7.16              | _8112_AD_DMA_Stop                                                | .77 |

| 7.17 | _8112_AD_INT_Start     |     |

|------|------------------------|-----|

| 7.18 | _8112_AD_INT_Status    | 79  |

| 7.19 | _8112_AD_INT_Stop      | 80  |

| 7.20 | _8112_AD_Timer         | 81  |

| 7.21 | _8112_TIMER_Start      | 82  |

| 7.22 | _8112_TIMER_Read       | 83  |

| 7.23 | _8112_TIMER_Stop       | 83  |

| Арре | endix A. Demo Programs | 85  |

| Warr | anty                   | 856 |

# How to Use This Guide

This manual is designed to help you use the ACL-8112. The manual describes how to modify various settings on the ACL-8112 card to meet your requirements. It is divided into seven chapters:

#### Chapter 1 Introduction

Gives an overview of the product features, applications, and specifications.

#### Chapter 2 Installation

Describes how to install the ACL-8112. The layout of the ACL-8112 is shown, the switch setting for base address, and jumper setting for analog input channel configuration, reference voltage setting, trigger source, interrupt level and DMA channel are specified.

#### Chapter 3 Signal Connection

Describes the connectors' pin assignment and how to connect the outside signal and devices with the ACL-8112.

#### Chapter 4 Registers

Describes the details of register format and structure of the ACL-8112, this information is very important for the programmers who want to control the hardware by low-level programming.

#### Chapter 5 **Operation Theory**

Describes how to operate the ACL-8112. The A/D, D/A, DIO and timer/counter functions are introduced. Also, some programming concepts are specified.

#### Chapter 6 Calibration & Utility

Describes how to calibrate the ACL-8112 for accurate measurement.

#### Chapter 7 C Language Library

Describes how to program the ACL-8112 by using the C language library in DOS environment.

#### Appendix A Demo Program

Describes some demonstration programs.

# 1

# Introduction

The ACL-8112 is a high performance, high speed multi-function data acquisition card for IBM PC or compatible computers.

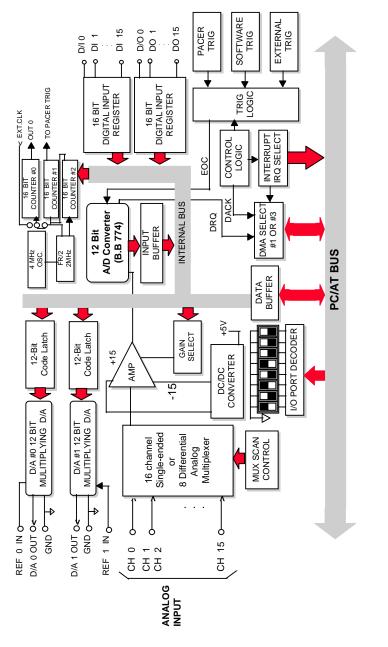

The ACL-8112 series is designed to combine all data acquisition functions, such as A/D, D/A, DIO and timer/counter into a single board, The high-end specifications of the card makes it ideal for a wide range of applications requiring high speed. Figure 1.1 shows the block diagram of the ACL-8112.

The ACL-8112 Series consists of three models, the ACL-8112HG, ACL-8112DG and ACL-8112PG. The ACL-8112HG provides special high-gain programmable instrument amplifier for low level input applications, such as measurement of thermo-coupling signals. The ACL-8112DG provides high speed sampling rates (up to 100 KHz) at all gains (x1, x2, x4, and x8) and the ACL-8112PG provides 16 single-ended inputs with sampling up to 100 KHz with 5 levels of gain (x1, x2, x4, x8, x16)

All ACL-8112 Series feature 16 single-ended inputs or 8 differential inputs, 2 12-bit double-buffered analog outputs, 16 digital inputs and 16 digital outputs, and one timer/counter channel.

Figure 1.1 ACL - 8112 BLOCK DIAGRAM

#### 1.1 Features

The ACL-8112 series Enhanced Multi-function Data Acquisition Card provides the following advanced features:

- AT-Bus

- 16 single-ended or 8 differential analog input channels for ACL-8112DG/HG, 16 single-ended for ACL-8112PG

- Bipolar or unipolar input signals for ACL-8112DG/HG, bipolar for ACL-8112PG

- Programmable gain

- High gain for ACL-8112HG:( x0.5, x1, x5, x10, x50, x100, x500, x1,000)

- Normal gain for ACL-8112DG (x0.5, x1, x2, x4, x8)

- 5 Levels programmable gain for ACL-8112PG (x1, x2, x4, x8, x16), x0.5 gain can be set by jumper

- On-chip sample & hold

- Two 12-bit monolithic multiplying analog output channels

- 16 digital output channels

- 16 digital input channels

- 3 programmable 16-bit down counters

- Programmable sampling rate of up to 100KHz

- Three A/D trigger modes: software trigger, programmable pacer trigger, and external pulse trigger

- AT interrupt IRQ capability: 9 IRQ levels (IRQ3~IRQ15) are jumper selectable

- Integral DC-to-DC converter for stable analog power source

- 37-pin D-type connector

- Compact size: half-size PCB

# 1.2 Applications

- Industrial and laboratory ON/OFF control

- Energy management

- Annunciation

- 16 TTL/DTL compatible digital input channels

- Security controller

- Product test

- Period and pulse width measurement

- Event and frequency counting

- Waveform and pulse generation

- BCD interface driver

## 1.3 Specifications

- Analog Input (A/D)

- Converter: ADS774 or equivalent, successive approximation type

- Resolution: 12-bit

- Number of channels:

- ACL-8112DG/HG: 16 single-ended or 8 differential

ACL-8112PG: 16 single-ended

- Input Range: (Programmable)

- ACL-8112HG:

Bipolar : ±10V,± 5V,±1V,±500 mV,±100mV,±50mV, ±10mV, ±5mV Unipolar: 0~10V, 0~1V, 0~0.1V, 0~0.01V

• ACL-8112DG:

Bipolar : ±10V, ± 5V, ±2.5V, ±1.25V, ±0.625 Unipolar: 0~10V, 0~5V, 0~2.5V, 0~1.25V

#### • ACL-8112PG:

Bipolar :  $\pm$  10V ,  $\pm$  5V,  $\pm 2.5$  V,  $\pm 1.25$  V,  $\pm 0.625$  V

Or

Bipolar : ± 5V, ±2.5V, ±1.25V, ±0.625V, ±0.3125V

- Conversion Time: 8 μ sec

- **Overvoltage protection:** Continuous ± 35V maximum

- Accuracy:

(ACL-8112HG)

| GAIN = 0.5, 1    | 0.01% of FSR ±1 LSB         |

|------------------|-----------------------------|

| GAIN = 5, 10     | 0.02% of FSR ±1 LSB         |

| GAIN = 50, 100   | 0.04% of FSR <u>+</u> 1 LSB |

| GAIN = 500, 1000 | 0.04% of FSR $\pm$ 1 LSB    |

#### (ACL-8112DG)

| GAIN = 0.5, 1 | 0.01% of FSR ±1 LSB         |

|---------------|-----------------------------|

| GAIN = 2, 4   | 0.02% of FSR <u>+</u> 1 LSB |

| GAIN = 8      | 0.04% of FSR ±1 LSB         |

#### (ACL-8112PG)

| GAIN = 0.5, 1, 2, 4 | 0.015% of FSR ±1 LSB |

|---------------------|----------------------|

| GAIN = 8, 16        | 0.02% of FSR ±1 LSB  |

- Input Impedance: 10 MΩ

- AD conversion trigger modes: Software, Pacer, and External trigger

- Data Transfer: Pooling, DMA, Interrupt

- Sampling Rate:

- 100 KHz maximum for single channel

- 100 KHz maximum for multiplexing on ACL-8112PG

- 20 KHz maximum for multiplexing on ACL-8112DG/HG

#### Analog Output (D/A)

- Converter: DAC7541 or equivalent, monolithic multiplying

- Number of channels: 2 double-buffered analog outputs

- Resolution: 12-bit

#### • Output Range:

Internal reference: (unipolar) 0~5V or 0~10V External reference: (unipolar) max. +10V or -10V

- Settling Time: 30 µ sec

- Linearity: ±1/2 bit LSB

- Output driving capability: <u>+</u>5mA max.

- Digital I/O (DIO)

- Number of channels: 16 TTL compatible inputs and outputs

#### • Input Voltage:

Low: Min. 0V; Max. 0.8V

High: Min. +2.0V

#### • Input Load:

Low: +0.5V @ -0.2mA max.

High: +2.7V @+20mA max.

#### • Output Voltage:

Low: Min. 0V ; Max. 0.4V

High: Min. +2.4V

#### • Driving Capacity:

Low: Max. +0.5V at 8.0mA (Sink)

High: Min. 2.7V at 0.4mA(Source)

#### Programmable Counter

- **Device:** 8254

- **A/D pacer:** 32-bit timer( two 16-bit counter cascaded together) with a 2MHz time base

- Pacer Output: 0.00046 Hz ~ 100 KHz

- **Counter:** One 16-bit counter with internal 2MHz time base or external clock source

- General Specifications

- I/O Base Address: 16 consecutive address location

- Interrupt IRQ: IRQ3,5,6,7,9,10,11,12,15 (9 levels)

- **DMA Channel**: CH1 and CH3 (Jumper selectable)

- **Connector:** 37-pin D-type connector

- Operating Temperature: 0 °C ~ 55 °C

- Storage Temperature: -20 °C ~ 80°C

- **Humidity:** 5 ~ 95%, non-condensing

#### • Power Consumption:

ACL-8112DG/HG: +5 V @ 430 mA typical +12V @ 150 mA typical ACL-8112PG: +5 V @ 450 mA typical 12 V @ 150 mA typical

#### • Dimension:

ACL-8112DG/HG: 162mm(L) x 115mm(W) ACL-8112PG: 163 mm(L) x 123 mm(W)

# 1.4 Software Support

#### 1.4.1 Programming Library

For users who are writing their own programs, we provide MS-DOS Borland C/C++ programming library.

ACLS-DLL2 is the Development Kit for NuDAQ ISA-Bus Cards with Analog I/O for windows 3.1/95(98)/NT. ACLS-DLL2 can be used in many programming environments, such as VC++, VB, and Delphi. ACLS-DLL2 is included in the ADLINK CD. To use this package a license is required.

#### 1.4.2 LabView Driver

The ACLS-LVIEW includes the ACL-8112's Vis, which is used to interface with NI's LabView software package. The ACLS-LVIEW supports Windows-95(98)/NT. ACLS-LVIEW is included in the ADLINK CD. To use this package a license is required.

# 2

# Installation

This chapter describes how to install the ACL-8112 series products. Please use the following steps to install the product.

- Check what you have (section 2.1)

- Unpacking (section 2.2)

- Check the PCB and jumper location(section 2.3)

- Install the hardware and setup the jumpers and switches (section 2.4~2.12)

- Cabling with external devices (section 2.13)

### 2.1 What You Have

In addition to this User's Manual, the package includes the following items:

- ACL-8112 Enhanced Multi-function Data Acquisition Card

- ADLINK CD

If any of these items are missing or damaged, contact ADLINK or the dealer from whom you purchased the product. Save the shipping materials and carton in case you want to ship or store the product in the future.

**Note:** The utilities and libraries in the CD-ROM only support the ACL-8112 series under DOS environment. If you need to develop applications under Windows 3.1., Windows 95 or Windows NT, please contact our dealer for purchasing software development kit ACLS-DLL2.

## 2.2 Unpacking

The card contains electro-static sensitive components that can be easily be damaged by static electricity.

Therefore, the card should be handled on a grounded anti-static mat. The operator should be wearing an anti-static wristband, grounded at the same point as the anti-static mat.

Inspect the card module carton for obvious damages. Shipping and handling may cause damage to your module. Be sure there are no shipping and handling damages on the modules carton before continuing.

After opening the card module carton, extract the system module and place it only on a grounded anti-static surface with component side up.

Again, inspect the module for damages. Press down on all the socketed IC's to make sure that they are properly seated. Do this only with the module place on a firm flat surface.

Note: DO NOT ATTEMPT TO INSTALL A DAMAGED BOARD IN THE COMPUTER.

You are now ready to install your card.

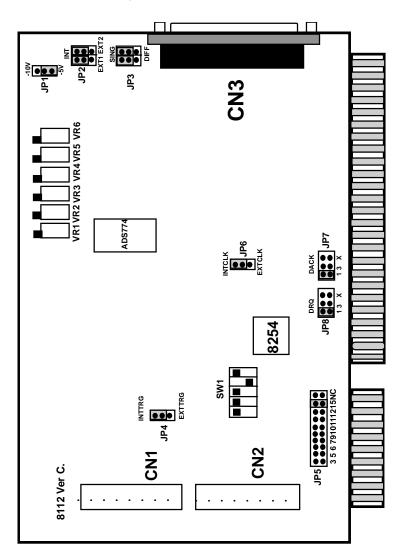

Figure 2.1-1 PCB Layout of the ACL-8112DG/HG Ver C.

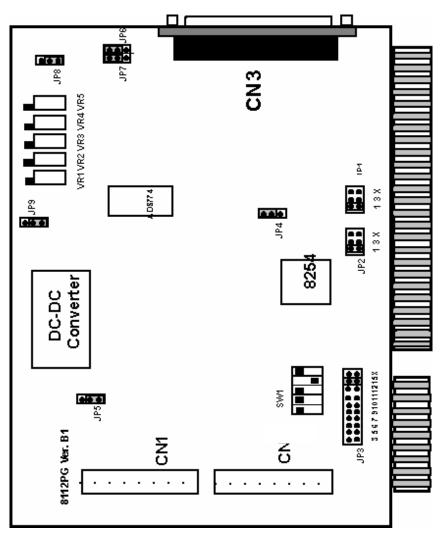

Figure 2.1-2 PCB Layout of the ACL-8112PG

## 2.4 Jumper and DIP Switch Description

You can change the ACL8112's channels and the base address by setting jumpers and DIP switches on the card. The card's jumpers and switches are preset at the factory. You can change the jumper settings for your own applications.

A jumper switch is closed (sometimes referred to as "shorted") with the plastic cap inserted over two pins of the jumper. A jumper is open when the plastic cap is inserted over one or no pin(s) of the jumper.

## 2.5 Base Address Setting

The ACL-8112 requires 16 consecutive address locations in the I/O address space. The base address of the ACL-8112 is restricted by the following conditions.

- 1. The base address must be within the range Hex 200 to Hex 3FF.

- 2. The base address should not conflict with any PC reserved I/O address. see Appendix A.

- **3.** The base address must not conflict with any add-on card on your own PC. Please check your PC before installing the ACL-8112.

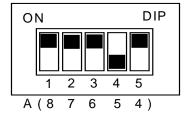

The ACL-8112's base address of registers is selected by an 6 positions DIP switch **SW1**. The default setting of base address is set to be *HEX 220*. All possible base address combinations are listed as Table 2.2. You may modify the base address if the address *HEX 220* has been occupied by another addon card.

SW1 : Base Address = Hex 220

Figure 2.2 Default Base Address Setting

| I/O port     |     | 1   | 2   | 3   | 4   | 5   |

|--------------|-----|-----|-----|-----|-----|-----|

| Address(Hex) | A9  | A8  | A7  | A6  | A5  | A4  |

| 200-20F      |     | ON  | ON  | ON  | ON  | ON  |

|              | (1) | (0) | (0) | (0) | (0) | (0) |

| 210-21F      |     | ON  | ON  | ON  | ON  | OFF |

|              | (1) | (0) | (0) | (0) | (0) | (1) |

| 220-22F      |     | ON  | ON  | ON  | OFF | ON  |

| (default)    | (1) | (0) | (0) | (0) | (1) | (0) |

| 230-23F      |     | ON  | ON  | ON  | OFF | OFF |

|              | (1) | (0) | (0) | (0) | (1) | (1) |

| :            |     |     |     |     |     |     |

| 300-30F      |     | OFF | ON  | ON  | ON  | ON  |

|              | (1) | (1) | (0) | (0) | (0) | (0) |

| :            |     |     |     |     |     |     |

| 3F0-3FF      |     | OFF | OFF | OFF | OFF | OFF |

|              | (1) | (1) | (1) | (1) | (1) | (1) |

#### Table 2.2 Possible Base Address Combinations

A0, ..., A9 corresponds to the PC Bus address lines A9 is fixed at "1".

How to define/determine the base address of the ACL-8112 ? DIP1 to DIP5 of SW1 corresponds to the PC bus address line A8 to A4 respectively. A9 is always 1 and A0~A3 are always 0. If you want to change the base address, you can only change the values of A8 to A4 (the shadow area of the table below). The following table is an example, of how to set a base address of *Hex 220*

| Base A | Address | : Hex 2 | 220 |    |    |    |    |    |    |

|--------|---------|---------|-----|----|----|----|----|----|----|

|        | 2       |         |     | 2  |    |    | (  | )  |    |

| 1      | 0       | 0       | 0   | 1  | 0  | 0  | 0  | 0  | 0  |

| A9     | A8      | A7      | A6  | A5 | A4 | A3 | A2 | A1 | A0 |

# 2.6 Analog Input Channel Configuration

(This section is for ACL-8112DG and ACL-8112HG only.)

The ACL-8112 offers 16 single-ended or 8 differential analog input channels. JP3 controls the analog input channel configuration. The setting of JP3 is specified in the following illustration.

| Single-ended<br>(default setting) | JP3 DIFF |

|-----------------------------------|----------|

| Differential Input                | JP3 DIFF |

Figure 2.3 Analog Input Channels Configuration

# 2.7 DMA Channel Setting

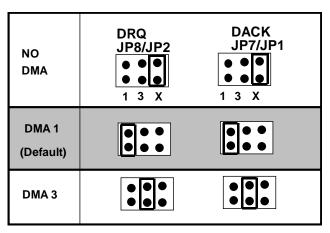

The A/D data transfer of the ACL-8112 is designed with DMA transfer capabilities. The setting of the DMA for channel 1 or channel 3 is controlled by JP7 and JP8 on the ACL-8112DG/HG, and JP1 and JP2 on the ACL-8112PG . Possible settings are shown below:

| Note: | On floppy disk only machine, we suggest you set the DMA to level 3.       |

|-------|---------------------------------------------------------------------------|

|       | If you have a hard disk installed in the computer, level 1 is preferable. |

Figure 2.4 DMA Channel Setting

# 2.8 Internal/External Trigger Setting

The A/D conversion trigger source of the ACL-8112 can come from an internal or external source. The internal or external trigger source is set by JP4 on the ACL-8112DG/HG and by JP5 on the ACL-8112PG, as shown on Figure 2.5. Note that there are two internal trigger sources, one is by software trigger and the other is by the programmable pacer trigger, which is controlled by the mode control register(see section 4.5).

| Internal Trigger<br>(default setting) | JP4 / JP5<br>INTTRG<br>EXTTRG |

|---------------------------------------|-------------------------------|

| External Trigger                      | JP4 / JP5<br>INTTRG<br>EXTTRG |

Figure 2.5 Trigger Source Setting

| Internal Clock           | JP6/JP4                       |

|--------------------------|-------------------------------|

| Source : 2MHz            | INTCLK                        |

| (default setting)        | EXTCLK                        |

| External Clock<br>Source | JP6 / JP4<br>INTCLK<br>EXTCLK |

Figure 2.6 Timer's Clock Source Setting

# 2.9 Clock Source Setting

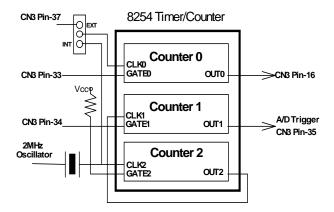

The 8254 programmable interval timer is used in the ACL-8112. It provides 3 independent 16-bit programmable down counters. The input of counter 2 is connected to a precision 2MHz oscillator which is the internal pacer. The input of counter 1 is cascaded from the output of counter 2. Channel 0 is free for user's applications. There are two selections for the clock source of channel 0: the internal 2MHz clock or an external clock signal from connector CN3 pin 37. The setting for the clock is shown in Figure 2.6.

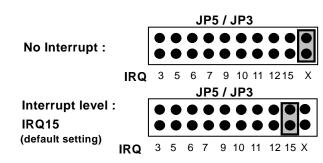

## 2.10 IRQ Level Setting

The ACL-8112 can connect to any one of the interrupt lines of the PC I/O channel. The interrupt line is selected by JP5 of ACL-8112DG/HG or JP3 of ACL-8112PG. If you wish to use the interrupt capability of ACL-8112, you must select an interrupt level and place the jumper in the appropriate position to enable the particular interrupt line.

The default interrupt level is IRQ15, which is selected by placing the jumper on the pins in row number 15. Figure 2.7 shows the default interrupt jumper setting IRQ15. You only remove the jumper from IRQ15 to other new pins, if you want to change to another IRQ level.

**Note:** Please note that no other add-on cards can shares the same interrupt level at the same time.

Figure 2.7 IRQ Level Setting

# 2.11 D/A Reference Voltage Setting

The D/A converter's reference voltage source can be internally or externally generated. The external reference voltage is connected via CN3 pin 31(*ExtRef1*) and pin 12(*ExtRef2*), see section 3.1. The D/A reference source of channel 1 and channel 2 are selected using JP2 for the ACL-8112DG/HG and JP6 and JP7 for the ACL-8112PG respectively. Possible settings are shown below:

|                     | JP2 or JP7 JP6 |

|---------------------|----------------|

| D/A CH1 is External |                |

| D/A CH2 is External | ExtRef1        |

|                     | JP2 or JP7 JP6 |

| D/A CH1 is External |                |

| D/A CH2 is Internal | ExtRef1        |

|                     | JP2 or JP7 JP6 |

| D/A CH1 is Internal |                |

| D/A CH2 is External | ExtRef1        |

|                     | JP2 or JP7 JP6 |

| D/A CH1 is Internal |                |

| D/A CH2 is Internal | ExtRef1        |

Figure 2.8 D/A Voltage Setting

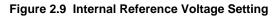

The internal voltage can be set to -5V or -10V which is selected by JP1 for the ACL-8112DG/HG and JP8 for the ACL-8112PG. Possible configurations are specified in Figure 2.9. Note that the internal reference voltage is used only when JP2 of the ACL-8112DG/HG or JP6 and JP7 of the ACL-8112PG is set to internal reference.

| Reference Voltage is<br>-5V (default setting) | -10V<br>• JP1 /<br>JP8<br>• JP8 |

|-----------------------------------------------|---------------------------------|

| Reference Voltage is<br>-10V                  | -10V<br>• JP1 /<br>JP8<br>• JP8 |

# 2.12 A/D Input Range Setting

(This section is for the ACL-8112PG only)

The A/D input range of the ACL-8112PG can be set to  $\pm 5V$  or  $\pm 10V$  using JP9.

| A/D Input Range is +/-<br>5V (default setting) | 10<br>• JP9<br>5 |

|------------------------------------------------|------------------|

| A/D Input Range is +/-<br>10V                  | 10<br>• JP9<br>5 |

3

# **Signal Connections**

This chapter describes the connectors of the ACL-8112. Signal connections between the ACL-8112 and external devices, such as daughter boards or other devices are also outlined.

## 3.1 Connectors Pin Assignment

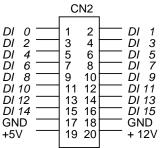

The ACL-8112 comes equipped with two 20-pin insulation displacement connectors - CN1 and CN2 and one 37-pin D-type connector - CN3. CN1 and CN2 are located on the board and CN3 is located at the rear plate.

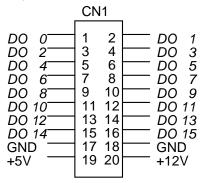

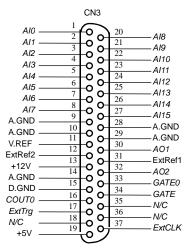

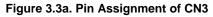

CN1 is used for digital output signals, CN2 is used for digital input signals and CN3 is used for analog input, analog output and timer/counter's signals. The pin assignment for each connector is illustrated in Figure 3.1 ~ Figure 3.3.

• CN2: Digital Signal Input (DI 0 - 15)

Figure 3.1. Pin Assignment of CN2

• **CN1:** Digital Signal Output (*DO 0 - 15*)

Figure 3.2. Pin Assignment of CN1

#### Legend:

*DO n*: Digital output signal channel n*DI n*: Digital input signal channel nGND: Digital ground  CN3: Analog Input/Output & Counter/Timer ( for single-ended connection: ACL-8112DG/HG/PG)

CN 3: Analog Input/Output & Counter/Timer (for differential connection:: ACL-8112DG/HG)

Figure 3.3b. Pin Assignment of CN3

#### Legend:

Aln: Analog Input Channel n (single-ended) AlHn: Analog High Input Channel n (differential) AlLn: Analog Low Input Channel n (differential) ExtRef n: External Reference Voltage for D/A CH n AOn: Analog Output Channel n ExtCLK: External Clock Input ExtTrig: External Trigger Signal CLK: Clock input for 8254 GATE: Gate input for 8254 COUT n: Signal output of Counter n V.ERF: Voltage Reference A.GND: Analog Ground GND: Ground

# 3.2 Analog Input Signal Connection

The ACL-8112 provides 16 single-ended or 8 differential analog input channels. The analog signal can be converted to digital value by the A/D converter. To avoid ground loops and obtain a more accurate measurement of the A/D conversion, it is quite important to understand the signal source type and how to choose the correct analog input mode: signal-ended or differential. The ACL-8112 allows for the configuration through jumpers.

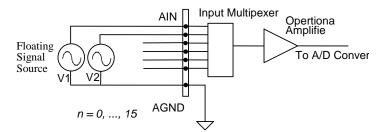

Single-ended Mode:

For single-ended mode, only one input is connected relative to ground and is suitable for connecting with a *floating signal source*. Floating source means it does not have any connection to ground. Figure 3.4 shows a single-ended connection. Note that when two or more floating sources are connected, the sources must be connected to common ground.

Figure 3.4 Floating source and single-ended

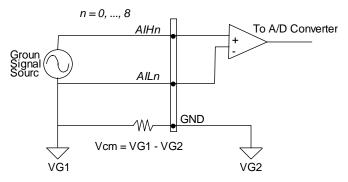

Differential input mode:

The differential input mode provides two inputs that respond to signal voltage differences between them. If the signal source is ground-referenced, the differential mode can be used to reduce ground loops. Figure 3.5 shows the connection for differential input mode. However, even if the signal source is locally grounded, the single-ended configuration can still be used when the Vcm ( Common Mode Voltage) is very small and the effect of ground loop is negligible.

Figure 3.5 Ground source and differential input

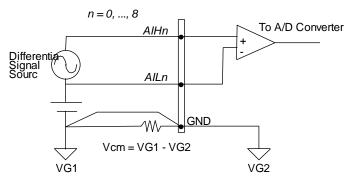

A differential mode must be used when the signal source is differential. A differential source means the ends of the signal are not grounded. To avoid dangerously high voltages between the local ground of the signal and the ground of the PC system, a shorted ground path must be connected. Figure 3.6 shows the connection for a differential source.

Figure 3.6 Differential source and differential input

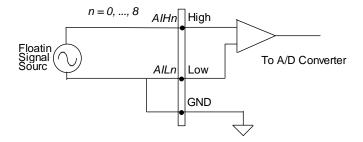

If your signal sources contain both a floating and a local ground, you should use the differential mode, with the floating signal source connected as Figure 3.7 .

Figure 3.7 Floating source and differential input

# 3.3 Analog Output Signal Connection

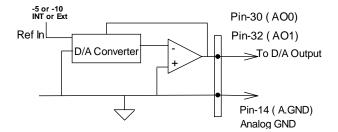

The ACL-8112 has two unipolar analog output channels. To make the D/A output connections from the appropriate D/A output, please refer Figure 3.8.

Figure 3.8 Connection of Analog Output Connection

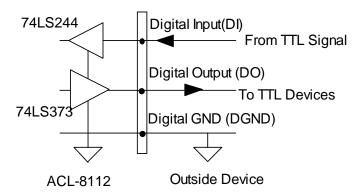

# 3.4 Digital I/O Connection

The ACL-8112 provides 16 digital input and 16 digital output channels through CN1 and CN2 on board. The digital I/O signals are fully TTL/DTL compatible. Details of the digital I/O signal specification can be referred to in section 1.3.

Figure 3.9 Digital I/O Connection

# 3.5 Timer / Counter Connection

The ACL-8112 has an interval 8254 timer/counter on board. It offers 3 independent 16-bit programmable down counters; counter 1 and counter 2 are cascaded together as a timer pacer trigger for A/D conversions and counter 0 is free for user applications. Figure 3.10 shows the 8254 timer/counter connection.

Figure 3.10 Block Diagram of 8254 Timer/Counter

The clock source of counter 0 can be internal or external, with the gate being controlled externally and the output sent to CN3. As for counter 1 and counter 2, the clock source is internally fixed, while the gate can be controlled externally and the output sent to CN3 too. All timer/counter signals are TTL compatible.

# 3.6 Daughter Board Connection

The ACL-8112 can be connected with any of the five following daughter boards, ACLD-8125, ACLD-9137, ACLD9182, ACLD9185, and ACLD9188. The functionality and connections are specified below.

# 3.6.1 Connect with ACLD-8125

The ACLD-8125 has a 37-pin D-sub connector, which can be connected to the ACL-8112HG through a 37-pin assemble cable. The most outstanding feature of this daughter board is the CJC ( cold junction compensation) circuit on board. You can directly connect a thermo-coupler to the ACL-8125 board.

## 3.6.2 Connect with ACLD-9137

The ACLD-9137 is a direct connector for the ACL-8112 card which is equipped with a 37-pin D-sub connector. This board provides a simple way for connecting simple applications that do not need complex signal conditioning before an A/D conversion is performed.

#### 3.6.3 Connect with ACLD-9182

The ACLD-9182 is a 16 channel isolated digital input board. This board is connected to CN1 of the ACL-8112 via a 20-pin ribbon cable. The advantage of this board is the 500Vdc isolation voltage that it provides, thus it can protect your PC system from damage when an abnormal input signal occurs.

## 3.6.4 Connect with ACLD-9185

The ACLD-9185 is a 16 channel SPDT relay output board. This board is connected to CN2 of the ACL-8112 via a 20-pin ribbon cable. By using this board, you can control external devices through digital output signals.

#### 3.6.5 Connect with ACLD-9188

The ACLD-9188 is a general purpose terminal board for all cards which comes equipped with a 37-pin D-sub connector.

# 4

# Registers

A detailed description of the registers and its structure for the ACL-8112 are specified in this chapter. This information is useful for programmers who wish to handle the card through low-level programming. Hence, a low level programming syntax is also introduced. This information can also help beginners learn how to operate the ACL-8112 in the shortest possible time.

# 4.1 I/O Port Address

The ACL-8112 requires 16 consecutive addresses in the PC I/O address space. Table 4.1 shows the I/O address of each register with respect to the base address. The function of each register is also listed.

| I/O Address | Read          | Write                   |

|-------------|---------------|-------------------------|

| Base + 0    | Counter 0     | Counter 0               |

| Base + 1    | Counter 1     | Counter 1               |

| Base + 2    | Counter 2     | Counter 2               |

| Base + 3    | Not Used      | 8254 Counter Control    |

| Base + 4    | A/D low byte  | CH1 D/A low byte        |

| Base + 5    | A/D high byte | CH1 D/A high byte       |

| Base + 6    | DI low byte   | CH2 D/A low byte        |

| Base + 7    | DI high byte  | CH2 D/A high byte       |

| Base + 8    | Not Used      | Clear Interrupt Request |

| Base + 9    | Not Used      | A/D Range Control       |

| Base + 10   | Not Used      | Channel MUX             |

| Base + 11   | Not Used      | Mode Control            |

| Base + 12   | Not Used      | Software A/D trigger    |

| Base + 13   | Not Used      | DO low byte             |

| Base + 14   | Not Used      | DO high byte            |

| Base + 15   | Not Used      | Not Used                |

Table 4.1 I/O Address

# 4.2 A/D Data Registers

The ACL-8112 series has a 12-bit resolution for each analog input channel, the digital data is store in the A/D data registers after an A/D conversion. The A/D data is put into two 8 bits registers. The lowest byte data (8 LSBs) are placed in address BASE+4 and the highest byte data (4 MSBs) are placed in address BASE+5. A DRDY bit is used to indicate the status of the A/D conversion. When the DRDY goes low, it means an A/D conversion is complete.

Address : BASE + 4 and BASE + 5 Attribute: read only Data Format:

| Bit    | 7   | 6   | 5   | 4    | 3    | 2    | 1   | 0   |

|--------|-----|-----|-----|------|------|------|-----|-----|

| BASE+4 | AD7 | AD6 | AD5 | AD4  | AD3  | AD2  | AD1 | AD0 |

| BASE+5 | 0   | 0   | 0   | DRDY | AD11 | AD10 | AD9 | AD8 |

AD11 .... AD0: Analog to digital data. AD11 is the Most Significant Bit(MSB). AD0 is the Least Significant Bit(LSB).

DRDY: Data Ready Signal.

- 1: A/D data is not ready

- 0: A/D conversion is completed.

It will be set to 1, when reading the low byte.

# 4.3 A/D Channel Multiplexer Register

This register is used to control the A/D channels. It's a write only register. When a channel number is written to the register, the multiplexer switches to another channel and waits until there's a conversion and switches again.

Address : BASE + 10 Attribute: write only Data Format:

| Data i onnat. | - |   |     |     |     |     |     |     |

|---------------|---|---|-----|-----|-----|-----|-----|-----|

| Bit           | 7 | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

| BASE+10       | Х | Х | CS1 | CS0 | CL3 | CL2 | CL1 | CL0 |

CLn: multiplexer channel number (n=0~3). CL3 is MSB, and CL0 is LSB.

CS0, CS1: Single-ended and Differential Selection (ACL-8112DG/HG only)

CS0 and CS1 are used to determine which MPC508A chip is selected. The MPC508A is used to multiplex between channels, when CS0 is set as 1, the analog input channels from 0 to 7 are selectable, and when CS1 is set to 1, channels 8 to 15 are selectable. When both CS0 and CS1 are set to 1, it means the analog inputs are in differential mode. The possible analog input channel selections combination is listed in the table below.

For ACL-8112PG, CS0 and CS1 always be zero, CL3~CL0 is used to select the 16 single-ended channels.

| Bit       | 7 | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|---|---|-----|-----|-----|-----|-----|-----|

| Channel   | Х | Х | CS1 | CS0 | CL3 | CL2 | CL1 | CL0 |

| S.E. CH0  | Х | Х | 0   | 1   | 0   | 0   | 0   | 0   |

| S.E. CH1  | Х | Х | 0   | 1   | 0   | 0   | 0   | 1   |

| S.E. CH2  | Х | Х | 0   | 1   | 0   | 0   | 1   | 0   |

| S.E. CH3  | Х | Х | 0   | 1   | 0   | 0   | 1   | 1   |

| S.E. CH4  | Х | Х | 0   | 1   | 0   | 1   | 0   | 0   |

| S.E. CH5  | Х | Х | 0   | 1   | 0   | 1   | 0   | 1   |

| S.E. CH6  | Х | Х | 0   | 1   | 0   | 1   | 1   | 0   |

| S.E. CH7  | Х | Х | 0   | 1   | 0   | 1   | 1   | 1   |

| S.E. CH8  | Х | Х | 1   | 0   | 1   | 0   | 0   | 0   |

| S.E. CH9  | Х | Х | 1   | 0   | 1   | 0   | 0   | 1   |

| S.E. CH10 | Х | Х | 1   | 0   | 1   | 0   | 1   | 0   |

| S.E. CH11 | Х | Х | 1   | 0   | 1   | 0   | 1   | 1   |

| S.E. CH12 | Х | Х | 1   | 0   | 1   | 1   | 0   | 0   |

| S.E. CH13 | Х | Х | 1   | 0   | 1   | 1   | 0   | 1   |

| S.E. CH14 | Х | Х | 1   | 0   | 1   | 1   | 1   | 0   |

| S.E. CH15 | Х | Х | 1   | 0   | 1   | 1   | 1   | 1   |

| D.I. CH0  | Х | Х | 1   | 1   | 0   | 0   | 0   | 0   |

| D.I. CH1  | Х | Х | 1   | 1   | 0   | 0   | 0   | 1   |

| D.I. CH2  | Х | Х | 1   | 1   | 0   | 0   | 1   | 0   |

| D.I. CH3  | Х | Х | 1   | 1   | 0   | 0   | 1   | 1   |

| D.I. CH4  | Х | Х | 1   | 1   | 0   | 1   | 0   | 0   |

| D.I. CH5  | Х | Х | 1   | 1   | 0   | 1   | 0   | 1   |

| D.I. CH6  | Х | Х | 1   | 1   | 0   | 1   | 1   | 0   |

| D.I. CH7  | Х | Х | 1   | 1   | 0   | 1   | 1   | 1   |

**S.E.**: Single-ended Analog Input **D.I.**: Differential Analog Input

# 4.4 A/D Range Control Register

The A/D range register is used to adjust the analog input ranges for the A/D channels. Two factor effects the input range: Gain and Polarity. For the ACL-8112PG, This register controls the PGA (programmable gain) directly and there is no Unipolar setting. When a different gain value is set, the analog input range is changed. For the ACL-8112DG/HG, both the PGA and polarity are controlled by this register. Table 4.2 shows the relationship between the register data and the A/D input range.

Address : BASE + 9 Attribute: write only Data Format:

| Bit    | 7 | 6 | 5 | 4 | 3  | 2  | 1  | 0  |

|--------|---|---|---|---|----|----|----|----|

| BASE+9 | Х | Х | Х | Х | G3 | G2 | G1 | G0 |

G0~G3: Gain / Range selection, G3 is not used for ACL-8112PG

| G3 | G2 | G1 | G0 | GAIN  | Bipolar<br>or<br>Unipolar | Input Range   |  |  |  |  |

|----|----|----|----|-------|---------------------------|---------------|--|--|--|--|

| 0  | 0  | 0  | 0  | 1     | Bipolar                   | ±5V           |  |  |  |  |

| 0  | 0  | 0  | 1  | 10    | Bipolar                   | ±0.5V         |  |  |  |  |

| 0  | 0  | 1  | 0  | 100   | Bipolar                   | ±0.05V        |  |  |  |  |

| 0  | 0  | 1  | 1  | 1,000 | Bipolar                   | ±0.005V       |  |  |  |  |

| 0  | 1  | 0  | 0  | 1     | Unipolar                  | 0V ~ 10V      |  |  |  |  |

| 0  | 1  | 0  | 1  | 10    | Unipolar                  | 0V ~ 1V       |  |  |  |  |

| 0  | 1  | 1  | 0  | 100   | Unipolar                  | 0V ~ 0.1V     |  |  |  |  |

| 0  | 1  | 1  | 1  | 1,000 | Unipolar                  | 0V ~ 0.01V    |  |  |  |  |

| 1  | 0  | 0  | 0  | 0.5   | Bipolar                   | ±10V          |  |  |  |  |

| 1  | 0  | 0  | 1  | 5     | Bipolar                   | ±1V           |  |  |  |  |

| 1  | 0  | 1  | 0  | 50    | Bipolar                   | <u>+</u> 0.1V |  |  |  |  |

| 1  | 0  | 1  | 1  | 500   | Bipolar                   | ±0.01V        |  |  |  |  |

| 1  | 1  | 0  | 0  | 1     | Unipolar                  | N/A           |  |  |  |  |

| 1  | 1  | 0  | 1  | 10    | Unipolar                  | N/A           |  |  |  |  |

| 1  | 1  | 1  | 0  | 100   | Unipolar                  | N/A           |  |  |  |  |

| 1  | 1  | 1  | 1  | 1,000 | Unipolar                  | N/A           |  |  |  |  |

(This table is only for the ACL-8112HG: High Gain Card)

Table 4.2-1 Function of the Gain Control Bits

| G3 | G2 | G1 | G0 | GAIN | Bipolar<br>or<br>Unipolar | Input Range |

|----|----|----|----|------|---------------------------|-------------|

| 1  | 0  | 0  | 0  | 0.5  | Bipolar                   | ±10V        |

| 0  | 0  | 0  | 0  | 1    | Bipolar                   | <u>+</u> 5V |

| 0  | 0  | 0  | 1  | 2    | Bipolar                   | ±2.5V       |

| 0  | 0  | 1  | 0  | 4    | Bipolar                   | ±1.25V      |

| 0  | 0  | 1  | 1  | 8    | Bipolar                   | ±0.625V     |

| 0  | 1  | 0  | 0  | 1    | Unipolar                  | 0V ~ 10V    |

| 0  | 1  | 0  | 1  | 2    | Unipolar                  | 0V ~ 5V     |

| 0  | 1  | 1  | 0  | 4    | Unipolar                  | 0V ~ 2.5V   |

| 0  | 1  | 1  | 1  | 8    | Unipolar                  | 0V ~ 1.25V  |

(This table is only for the ACL-8112DG: Low Gain Card)

#### Table 4.2-2 Function of the Gain Control Bits

For the ACL-8112PG, the maximum range is changed by hardware jumper configuration. JP9 is used to change the maximum analog input range form  $\pm$ 5V or  $\pm$ 10V. If JP9 is set as  $\pm$ 5V, the analog input range is listed as below.

| G3 | G2 | G1 | G0 | GAIN | Analog Input Range |

|----|----|----|----|------|--------------------|

| 0  | 0  | 0  | 0  | 1    | <u>+</u> 5V        |

| 0  | 0  | 0  | 1  | 2    | <u>+</u> 2.5V      |

| 0  | 0  | 1  | 0  | 4    | ±1.25V             |

| 0  | 0  | 1  | 1  | 8    | <u>+</u> 0.625V    |

| 0  | 1  | 0  | 0  | 16   | ±0.3125V           |

#### Table 4.2-3 Analog Input Range (max. is ±5V)

If JP9 is set as  $\pm 10V$ , the analog input range is listed as below

| G3 | G2 | G1 | G0 | GAIN | Analog Input Range |

|----|----|----|----|------|--------------------|

| 0  | 0  | 0  | 0  | 1    | ±10V               |

| 0  | 0  | 0  | 1  | 2    | <u>±</u> 5V        |

| 0  | 0  | 1  | 0  | 4    | <u>+</u> 2.5V      |

| 0  | 0  | 1  | 1  | 8    | ±1.25V             |

| 0  | 1  | 0  | 0  | 16   | ±0.625V            |

Table 4.2-4 Analog Input Range (max. is ±10V)

# 4.5 A/D Operation Mode Control Register

The A/D operation includes the analog signal conversion and the data transformation. This register controls the internal trigger mode and data transformation method. It is initialized by a software trigger or program polling transfer when the PC is reset or powered on. The details of the A/D operation are described in Chapter 5. There are four operation modes.

Address : BASE + 11

Attribute: write only

Data Format:

| Bit     | 7 | 6 | 5 | 4 | 3 | 2  | 1  | 0  |

|---------|---|---|---|---|---|----|----|----|

| BASE+11 | Х | Х | Х | Х | Х | S2 | S1 | S0 |

| S2 | S1 | S0 | Operation Mode Description                     |

|----|----|----|------------------------------------------------|

| 0  | 0  | 0  | Internal trigger is disable                    |

| 0  | 0  | 1  | software trigger and program polling (default) |

| 0  | 1  | 0  | timer pacer trigger and DMA transfer           |

| 1  | 1  | 0  | timer pacer trigger and interrupt transfer.    |

#### Note:

- 1. When your system is powered on or reset, the A/D operation will be initialized as " software trigger or program polling" mode.

- 2. No matter which mode is selected, the external trigger is available if JP4 is set as external trigger.

- 3. As long as the DMA mode is not used, the program polling mode is always selectable. The synchronization of the A/D conversion and data transfer should be of a concern when using program polling mode.

- 4. An interrupt will occur at the end of each conversion when the "timer pacer trigger and interrupt transfer" mode is selected. If you want to use the pacer trigger and interrupt transfer mode, you must enable the IRQ level.

# 4.6 Interrupt Status Register

The Interrupt Status Register is used to clear the interrupt status so a new interrupt can be generated. If the ACL-8112 is in interrupt data transfer mode, a hardware status flag will be set after each A/D conversion. You must clear the status flag by writing any data to this register, so that the ACL-8112 can generate a new or next interrupt if a new A/D conversion is to happen.

Address : BASE + 8

Attribute: write only

Data Format:

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|---|---|---|---|---|---|---|---|

| BASE+8 | Х | Х | Х | Х | Х | Х | Х | Х |

# 4.7 Software Trigger Register

If you want to generate a trigger pulse for the ACL-8112 to perform an A/D conversion, you need to write data to this register, this will trigger the A/D converter.

Address : BASE + 12

Attribute: write only

Data Format:

| Bit     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---|---|---|---|---|---|---|---|

| BASE+12 | Х | Х | Х | Х | Х | Х | Х | Х |

# 4.8 Digital I/O register

There are 16 digital input channels and 16 digital output channels provided by the ACL-8112. The address Base + 6 and Base + 7 are used for the digital input channels, and the address Base + 13 and Base + 14 are used for digital output channels.

Address : BASE + 6 & BASE + 7

Attribute: read only

Data Format:

| Bit      | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   |

|----------|------|------|------|------|------|------|-----|-----|

| Base + 6 | DI7  | DI6  | DI5  | DI4  | DI3  | DI2  | DI1 | DI0 |

| Base + 7 | DI15 | DI14 | DI13 | DI12 | DI11 | DI10 | DI9 | DI8 |

Address : BASE + 13 & BASE + 14

Attribute: write only

Data Format:

| Bit       | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   |

|-----------|------|------|------|------|------|------|-----|-----|

| Base + 13 | DO7  | DO6  | DO5  | DO4  | DO3  | DO2  | DO1 | DO0 |

| Base + 14 | DO15 | DO14 | DO13 | DO12 | DO11 | DO10 | DO9 | DO8 |

# 4.9 D/A Output Register

The D/A converter will convert the D/A output register data to an analog signal. The register data at address Base + 4 and Base + 5 are used for D/A channel 1and Base +6 and Base +7 for D/A channel 2.

Address : BASE + 4 & BASE + 5

Attribute: write only

Data Format: (for D/A Channel 1)

| Bit      | 7   | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

|----------|-----|-----|-----|-----|------|------|-----|-----|

| Base + 4 | DA7 | DA6 | DA5 | DA4 | DA3  | DA2  | DA1 | DA0 |

| Base + 5 | Х   | Х   | Х   | Х   | DA11 | DA10 | DA9 | DA8 |

Address : BASE + 6 & BASE + 7

Attribute: write only

Data Format: (for D/A Channel 2)

| Bit      | 7   | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

|----------|-----|-----|-----|-----|------|------|-----|-----|

| Base + 6 | DA7 | DA6 | DA5 | DA4 | DA3  | DA2  | DA1 | DA0 |

| Base + 7 | Х   | Х   | Х   | Х   | DA11 | DA10 | DA9 | DA8 |

DA0 is the LSB and DA11 is the MSB of the 12 bits data. X: don't care

**Note:** The D/A registers are "*double buffered*" so that the D/A analog output signals will not updated until the second (*high*) byte contains data or written to. This will ensure a single step transition for a D/A conversion.

# 4.10 Internal Timer/Counter Register

Two 8254 counters are used for periodical triggering of the A/D converter, with one left for user applications. The 8254 occupies 4 I/O address locations in the ACL-8112 as listed blow. Users may refer to NEC's or Intel's data sheet for full detail of the 8254. Summarized information is specified in Appendix B.

Address : BASE + 0 ~ BASE + 3

Attribute: read / write

Data Format:

| Base + 0 | Counter 0 Register (R/W) |

|----------|--------------------------|

| Base + 1 | Counter 1 Register (R/W) |

| Base + 2 | Counter 2 Register (R/W) |

| Base + 3 | 8254 CONTROL BYTE        |

# 5

# **Operation Theory**

The operation theory of the ACL-8112 card is described in this chapter. The function description include the A/D conversion, D/A conversion, digital I/O and counter / timer. The operation theory can help you understand how to manipulate or program the ACL-8112.

# 5.1 A/D Conversion

Before programming the ACL-8112 to perform an A/D conversion, you need to understand the following issues: